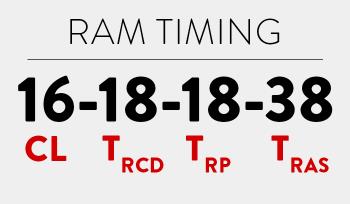

内存时序(英语:Memory timings或RAM timings)是描述同步动态随机存取存储器(SDRAM)性能的四个参数:CL、TRCD、TRP和TRAS,单位为时钟周期。最小时间是根据规范设置的,因此可以为每个DDR规范读取尽可能快的RAM时间表。

我们以时钟周期来度量内存时序,零售商列出的时间是由破折号分隔的四个数字,如16-18-18-38。数字越小,速度越快。

第一个数字:CAS延迟(CL)

内存响应CPU所需的时间是CAS延迟(CL),但是不能孤立地考虑CL。这个公式将CL时间转换为纳秒,基于RAM的传输速率:

(CL/转移率)x2000

因此,如果RAM的CL较短,则较慢的RAM实际上可以具有较低的实际延迟。

第二个数字:TRCD

RAM模块使用基于网格的寻址设计,行号和列号的交集表示特定的内存地址。行地址到列地址延迟(TRCD)测量在内存中输入新行和开始访问其中的列之间的最小延迟,您可以将它看作是RAM“到达”地址所花费的时间,从先前不活动的行接收第一个位所需的时间是TRCD + CL。

第三个数字:TRP

行预充电时间(TRP)测量在内存中打开新行所涉及的延迟,从技术上讲,它度量了将precharge命令发出到闲置(或关闭)一行与激活命令发出到打开另一行之间的延迟。它通常和第二个数相同。相同的因素影响这两个操作的延迟。

第四个数字:TRAS

行活动时间(TRAS)测量行必须保持打开状态以正确写入数据的最小循环数,从技术上讲,它度量了激活命令与在同一行发出预充电命令之间的延迟,或者是打开和关闭该行之间的最短时间。对于SDRAM模块,TRCD + CL计算TRAS。

如何计算内存时序?

内存时序可以通过CPU-Z或BIOS/UEFI等软件在机器或模块上找到, RAM模块的全称如下:

DDR4 3200 (PC4 25600)

DDR4描述了与芯片兼容的DDR的生成,相同的数字(2,3,4)出现在PC号码中,描述的是相同的东西。

第一个四位数,在我们的示例中为3200,通常表示RAM的时钟速度(以兆赫为单位),这个数字实际上报告了以每秒兆位传输速率为单位的数据速率。

在DDR RAM中,实际的时钟速度是数据速率的一半——在我们的例子中是1600mhz,尽管在RAM内部时钟速度400mhz的基础上通过乘法预取位来提高。

但是由于DDR每时钟周期传输两次数据,因此有效时钟速度可以说是实际时钟速度的两倍。因此,数据率是有效的一样,RAM的时钟速度在兆赫。

在我们的示例中,PC数字25600显示了以兆字节每秒(MB/s)为单位的传输速率。通过将数据速率(以megatransfers为单位)乘以I/O总线的宽度(在所有现代主板中为64位),我们可以确定可能的最大传输速率:

每秒3200兆位传输x 64位/8位/字节= 25600 MB/s

每个数字独立地告诉你RAM的速度有多快,但这两个数字提供了相同的信息,只是形式不同。